# **Design Note**

## UC3726 / UC3727 IGBT Isolated Driver Pair Evaluation Kit Testing Procedure

by: Bill Andreycak

The UC3726/UC3727 IGBT isolated driver pair evaluation kit is available for design engineers to verify the performance and functionality of this unique solution for isolated gate drive applications. Also relevant are datasheets for each IC and Unitrode Application Note U-143A describing each device's features, operation, programming and operational waveforms. A copy of Design Guide DG-200A containing Design Note DN-57 which addresses power dissipation issues, and a simplified test procedure for the evaluation kit is also beneficial. Users should take the time to familiarize themselves with the numerous performance features and fault protection options available with these devices for a variety of applications. This general Testing Procedure is usable for the UC3726/UC3727 Evaluation Kit as well as for debugging any prototype circuits or first run printed circuit boards. Refer to Figure 15 of Application Note U-143A for a complete circuit schematic and Table 1 for the List of Materials.

#### **Laboratory Equipment Needed:**

Oscilloscope

Power Supply to provide +30 VDC / 100mA

Signal or pulse generator

Test Leads

#### **Laboratory Test Procedure**

- \*\* Turn off all equipment prior to making any connections and verify that there is a single electrical ground connected to "earth" ground for all equipment.

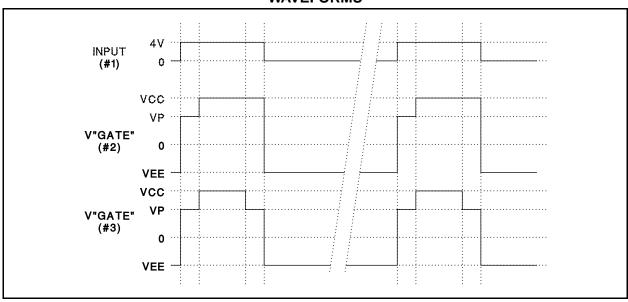

- Configure the pulse generator to output a square wave pulse train with an amplitude of 4VDC at a frequency of 10kHz and a duty cycle of 10% (10ms on-time). See waveform #1 for reference.

- 2. Make the following connections to the 8 pin header connector near U1 (UC3726):

| Signal                           | Connector<br>Pin |

|----------------------------------|------------------|

| +30VDC                           | 7                |

| Ground (return)                  | 8                |

| Pulse generator (+) output       | 4                |

| Pulse generator (-) output (GND) | 8                |

- \* Note that the header pin numbers do NOT correspond to the same IC pin numbers.

- 3. Make the following connections to the isolated side circuitry the opposite edge of the printed circuit board near U2 (UC3727):

### **WAVEFORMS**

Design Note DN-60

- A. Connect the "COLLECTOR" pin to the "EMITTER" pin using a jumper wire with clip leads.

- B. Connect the "EMITTER" pin to the ground connection at pin 8 of the header near U1.

- C. Connect the oscilloscope ground to circuit ground at the 8 pin header, pin 8.

- D. Connect the oscilloscope probe to the "GATE" pin near U2.

### **Testing Procedure**

- 1. Apply +30 VDC power to the evaluation kit

- 2. Turn ON the pulse generator

- Verify Waveform #2 on the scope at the "GATE" pin.

- Remove the test clip connection from the "COL-LECTOR" pin

- 5. Verify Waveform #3 on the scope at the "GATE" pin.

- Slowly increase the on-time (duty cycle) of the pulse generator until the "GATE" waveform latches off and remains at approximately –9VDC.

- 7. Reconnect the test lead to the "COLLECTOR" pin (from the "EMITTER")

- 8. Verify that the "GATE" waveform remains at approximately –9VDC.

- 9. Reduce the on-time (duty cycle) of the pulse generator back to 10μsec (10%).

- Briefly connect header pins 6 and 2 (Vlogic to Freset)

- Verify Waveform #2 on the scope at the "GATE" pin.

This concludes the basic testing of the UC3726/ UC3727 IGBT Evaluation Kit through verification of the gate drive waveforms. Verify isolation between the "low" and "high" side of the evaluation kit before testing in an isolated application circuit. Beware of ground loops and nonisolated power source. Whenever in doubt, use a low current (<1/4A) fuse in series with any test leads or equipment ground connections to prevent damage. The fuse will blow with any current flowing due to the attempted connections being nonisolated. Observe proper safety precautions as high voltage may be present in many IGBT applications. For complete operational details of the ICs, please refer to the datasheets and Applications literature.